# FPGA IMPLEMENTATION THROUGH SMART CAR SECURITY SYSTEM

Vijaykumar Chiluveru<sup>\*</sup>

M.Ramakrishna\*\*

## Abstract—

The main aim of this project is to offer an advanced security system in CAR, which consists of a face detection subsystem, a GPS module, a GSM module and a control platform. The face detection subsystem can detect faces in cars during the period in which nobody should be in the car, and make an alarm loudly or soundlessly. The other modules transmit necessary information to users and help to keep eyes on cars all the time, even when the car is lost. In today's world, many new techniques such as biometric recognition, image processing technique, and communication technique and so on, have been integrated into car security systems. At the same time, the amount of car lost is also increasing. Traditional car security systems depend on many sensors and cost is also high. When one car is lost, no more feedback could be available to help people to find it back. This system prototype is build on the base of the Field programmable Gate Array (FPGA) platform which controls all the processes. This results in a simple, cost effective, and flexible system, making it a good candidate for future smart home solutions.

**Keywords**— a Web cam, a GPS module, a GSM module and a control platform (Spartan FPGA *Kit*).

<sup>\*\*</sup> Associate Prof. Department of Electronics and communication engineering Jyothishmathi Institute of Technology & Sciences, Karimnagar, JNTU Hyderabad, India

http://www.ijmra.us

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A. International Journal of Engineering & Scientific Research

## I. INTRODUCTION

In this proposed embedded car security system, FDS (Face Detection System) is used to detect the face of the driver and compare it with the predefined faces. For example, in the night when the car's owner is sleeping and someone theft the car then FDS obtains images by one tiny web camera which can be hidden in the car. FDS compares the obtained image with the predefined images if the image doesn't match, then the information is sent to the owner through MMS. So now owner can obtain the image of the thief in his mobile as well as he can trace the location through GPS, with FPGA as the core, the new intelligent vehicle security system integrated a lot of hardware modules such as video capture, GPS positioning and wireless transmission, the design of the system software used the embedded software developing platform on. By the hardware/software co-design, the new intelligent vehicle security system implemented the functions of video capturing, GPS positioning and wireless transmission met the needs of vehicle owners about Vehicle Security. This paper presents a cost-effective solution that uses a Field **Programmable Gate** Array (FPGA) controller at the core of the system to provide the security for the car system. Moreover, the controller interfaces to a mobile device through the GSM Modem communications port to allow monitoring, configuration, and switching of devices. This allows the user to set the home environment according to the personal needs. This paper is organized as follows: Section II gives some background on systems found in literature. Section III provides an overview of the system developed, while Section IV presents the implementation of a prototype. Section V gives the obtained test results, while a final conclusion is drawn in Section VI.

## II. BACKGROUND WORK

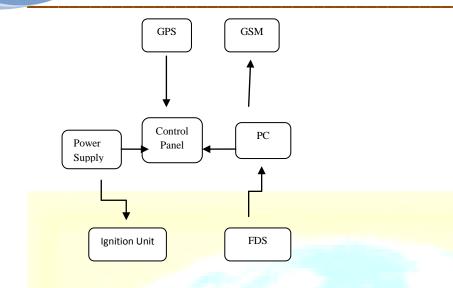

As shown in the figure 1, this system builds a new intelligent vehicle checking system based on FPGA embedded processing technology, processing technology of digital videos, vehicle identification technology, GSM wireless mobile telecommunication technology, GPS positioning technique, implements the security to vehicles. This system has the following features:

## Image Capture:

When the system works, the camera in the car capture the Image of driver automatically and saves it in the video buffer.

## FPGA-based Xilinx ISE:

The ISE is termed to the heart of System. It is designed based on a low power 32-bit FPGA. It is a high performance and low cost solution for network applications.

#### GPS module:

The system can correctly send the position of vehicle to the server center by GPS positioning. The GPS module obtains the precise locality by parsing received GPS signal.

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A.

> International Journal of Engineering & Scientific Research http://www.ijmra.us

ISSN: 2347-653

Figure 1. Block diagram of the system

#### GSM module:

A GSM modem is a wireless modem that works with a GSM wireless network. A wireless modem behaves like a dial-up modem. The main difference between them is that a dial-up modem sends and receives data through a fixed telephone line while a wireless modem sends and receives data through radio waves. The GSM module can send the information out by SMS (Short Message Service) message, including realtime position of the "lost" car and even the images of "the driver".

## **III. SYSTEM DESIGN**

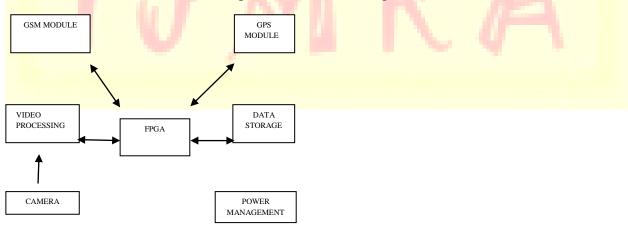

Smart vehicle Security system is composed of FPGA based peripheral equipment, and image capture, GPS positioning module, wireless telecommunication module and remote control receiver. The detailed hardware composition is shown in figure 2

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A.

> International Journal of Engineering & Scientific Research http://www.ijmra.us

# A. FPGA

A field-programmable gate array is a semiconductor device containing programmable logic components called "logic blocks", and programmable interconnects. Logic blocks can be programmed to perform the function of basic logic gates such as AND, and XOR, or more complex combinational functions such as decoders or mathematical functions. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory. A hierarchy of programmable interconnects allows logic blocks to be interconnected as needed by the system designer, somewhat like a one-chip programmable breadboard. Logic blocks and interconnects can be programmed by the customer or designer, after the FPGA is manufactured, to implement any logical function-hence the name "fieldprogrammable". FPGAs are usually slower than their application-specific integrated circuit (ASIC) counterparts, cannot handle as complex a design, and draw more power (for any given semiconductor process). But their advantages include a shorter time to market, ability to reprogram in the field to fix bugs, and lower non-recurring engineering costs. Vendors can sell cheaper, less flexible versions of their FPGAs which cannot be modified after the design is committed. The designs are developed on regular FPGAs and then migrated into a fixed version that more resembles an ASIC.

## FEATURES OF FPGA:

Very low cost, high-performance logic solution for high-volume, consumer-oriented applications:

- Densities as high as 74,880 logic cells

- Up to 784 I/O pins

- 622 Mb/s data transfer rate per I/O

- 18 single-ended signal standards

- 6 differential I/O standards including LVDS, RSDS

- Termination by Digitally Controlled Impedance

- Signal swing ranging from 1.14V to 3.45V

- Double Data Rate (DDR) support

- -Logic resources

- Abundant logic cells with shift register capability

- Wide multiplexers

- Fast look-ahead carry logic

- Dedicated 18 x 18 multipliers

- Up to 1,872 Kbits of total block RAM

- Up to 520 Kbits of total distributed RAM

- Digital Clock Manager (up to four DCMs)

- Clock skew elimination

- Eight global clock lines and abundant routing

## **B. IMAGE RECOGNITION AND PROCESSING**

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A.

In this embedded smart car security system, FDS (face detection subsystem) aims at detect somebody's face in the car during the time in which nobody should be in the car, FDS obtains images by one tiny digital camera which can be hidden easily in somewhere in one car.FDS is used to detect the face of the driver and compare it with the predefined face, whenever person enters in car FDS obtains images of that person by one web camera. FDS compares the obtained image with the predefined images if the image doesn't match then the information is send to the owner through MMS.

## C. GPS MODULE

The GPS module can receive the data by connected to FPGA development-board URAT0 through RS232 port. When the FPGA chip sends the instruction AT to GPS module, the GPS module starts receiving the data and saves it into memory. This instruction sends the region information with the vehicle license information to the support-server center through GSM net. Because the system is based on GPS data which is sent through GPRS net, it must be initialed at first. The initial instructions are following: Reset User settings initialized Following are the some instructions that are associated with GPS module and are useful in the system design.

AT+ID=X: this instruction is used to set the terminal address. Each device must be set the address which indicates its ID, the default ID is 139XXXXXXXX. The default address is the SIM card mobile phone number which contains 11 numbers, the address can be changed as required.

AT+IP=? this instruction is used to inquire the IP address. AT+PORT=X:this instruction is used to set the port

number of the application software in surveillance center server.

AT+PORT=? this instruction is used to inquire the port number.

$AT+HTH=X \square AT+HTH=? \square$  this instruction is used to set and inquire the time intervals of the GPS positioning information which the terminals send automatically. The unit of the time interval is second.

and does not need changing usually.

$AT+APN=X, AT+APN=? \Box$  this instruction is used to set and inquire the connect port of GPRS telecommunication. The default value is CMNET.

$AT+AGREE=X, AT+AGREE=? \Box$  this instruction is used to set and inquire the net communication protocol. The default value is TCP protocol. The terminal on car supports the UDP and the TCP protocol. Users can change the protocol as needs.

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A.

## **D.GSM MODEM**

A GSM modem is a wireless modem that works with a GSM wireless network. A wireless modem behaves like a dial-up modem. The main difference between them is that a dial-up modem sends and receives data through a fixed telephone line while a wireless modem sends and receives data through radio waves. A GSM modem can be an external device or a PC Card / PCMCIA Card. Typically, an external GSM modem is connected to a computer through a serial cable or a USB cable. A GSM modem in the form of a PC Card / PCMCIA Card is designed for use with a laptop computer. It should be inserted into one of the PC Card / PCMCIA Card slots of a laptop computer. Like a GSM mobile phone, a GSM modem requires a SIM card from a wireless carrier in order to operate. As mentioned in earlier sections of this SMS tutorial, computers use AT commands to control modems. Both GSM modems and dial-up modems support a common set of standard AT commands. You can use a GSM modem just like a dial-up modem. In addition to the standard AT commands, GSM modems support an extended set of AT commands. These extended AT commands are defined in the GSM standards. With the extended AT commands, you can do things like:

- Reading, writing and deleting SMS messages.

- Sending SMS/MMS messages.

- Monitoring the signal strength.

- Monitoring the charging status and charge level of the battery.

- Reading, writing and searching phone book entries.

## IV SOFTWARE DESIGN

Following are the different software's used to design a smart car security system

## A.XILINX - ISE:

Xilinx software is the leading vendor for 8/16-bit development tools. Xilinx software is represented worldwide in more than 40 countries, since the market introduction in 1988; the Xilinx C51 compiler is the de facto industry standard and supports more than 500 current device variants. Now, Xilinx software offers development tools for FPGA. Xilinx software makes C compilers, macro assemblers, real-time kernels, debuggers, simulators, integrated environments, and evaluation boards for 8051, 251, ARM and XC16x/C16x/ST10 microcontroller families.

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A. International Journal of Engineering & Scientific Research http://www.ijmra.us

ISSN: 2347-6532

## **B. VHDL**

Entity declaration input output to module (STD LOGIC)

```

entity counter is

Port ( CLK : in STD_LOGIC;

CLR : in STD_LOGIC;

DOUT : out STD_LOGIC_VECTOR (7 downto 0));

end counter;

```

#### signals declaration wires

signal value: std\_logic\_vector(7 downto 0);

concurrent assignments

$c \ll a$  and b;

conditional assignments => multiplexers

c <= a when sw='1' else b;

process declaration, concurrent functions, synchronous logic.

#### component declaration

```

component counter is

Port ( CLK : in STD_LOGIC;

CLR : in STD_LOGIC;

DOUT : out STD_LOGIC_VECTOR (7 downto 0));

end component counter;

```

```

counter_inst: component counter

port map(

CLK => CLK,

CLR => CLR,

DOUT => counter_value

);

```

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A.

International Journal of Engineering & Scientific Research http://www.ijmra.us

## C.MATLAB

This is the tool used for the image recognition and image processing. Using this code captured image is compared with the previously stored images and the result is given to processor whether person is authenticated or not.

## **D.VISUAL BASICS 6.0**

This is the visual basics 6.0 tool used to design the visual scripting webpage. The code written in a single webpage of window in the visual basic template. It is compared with the previously webpage and the result is given to processor whether person is authenticated details are stored or not in the database.

## V. RESULTS

VHDL test benches were designed to test all the developed VHDL code both at block level and at top level before downloading the synthesized code on the FPGA. The waveforms were checked to verify correct operation, both states and timings, of the hardware. The devices connected to the FPGA were also tested by forcing outputs and inputs and checking the functionality. All interfaced circuits functioned as expected. The communications channel had to be tested as well. A serial port monitoring program installed on a PC was used for this. A GSM wavecom was connected to the PC and the communication between mobile phone and the PC, the PC and the FPGA controller were tested. This was done by sending GSM commands and monitoring the replies. Once the controller and the GSM connection were tested, the whole system was tested exhaustively by sending commands and reading and noting the results. Images of the GPS wavecom screen are shown in Figure 3, while a image of the system which involves the central FPGA controller and the interface circuits is shown in Figure 4.

Figure 3. GSM Modem

Figure 4. FPGA controller and interfacing circuit

http://www.ijmra.us

## VI. CONCLUSION

From this we implement image-recognition techniques that can provide the important functions required by advanced intelligent Car Security, to avoid vehicle theft and protect the usage of unauthenticated users. Secured and safety environment system for automobile users and also key points for the investigators can easily find out the hijackers image. We can predict the theft by using this system in our day to day life. This project will help to reduce the complexity and improve security, also much cheaper and 'smarter' than traditional ones. Because of the flexibility of embedded system, the embedded smart car security system is extendable for special purposes. The System offers a widely communication bandwidth with the car control system to change data and information, and new functional modules can be easily added to the system to upgrade and enhance it.

## **REFERENCES**

[1] Joseph A. O'Sullivan, Robert Pless, "Advances in Security Technologies: Imaging, Anomaly Detection, and Target and Biometric Recognition", Microwave Symposium IEEE/MTT-S International Volume, Page(s):761 – 764, 2007.

[2] Viola P, Jones M, "Rapid Object Detection using a Boosted Cascade of Simple Features" Proceedings of the 2001 IEEE

Computer Society Conference on Computer Vision and Pattern Recognition, p511, 2001

[3]Jian Xiao "Haidong Feng. "A Low-cost Extendable Framework for Embedded Smart Car Security System" Proceedings of the 2009 IEEE International Conference on Networking, Sensing and Control, Okayama, Japan, March 26-29, 2009

[4] Lien hart R, Kuranov A, Pisarevsky, "Empirical analysis of detection cascades of boosted classifiers for rapid object detection" Technical report, MRL, Intel Labs, 2002.

[5] Viola P, Jones M, "Fast and robust classification using asymmetric AdaBoost and a detector cascade" NIPS 14, 2002.

[6] Lotufo R.A., Morgan A.D., Johnson A.S.Automatic numberplate recognition. Proceedings of image Analysis for transport applications, IEE Colloquium, 1990(6):1-6.

[7] K.W.Dickinson, C.L.Wan, Road traffic monitoring using the Trip system.IEEE 2nd int.Conf.Road Traffic Monitoring, 1989-02:56-60.

[8] A.S.Johnson,B.M.Bird.Number-; pate matching for automatic vehicle identification.Proceedings of electronic image and image processing in security and forensic science, IEEE Colloquium, 1990(4):1-8.

A Monthly Double-Blind Peer Reviewed Refereed Open Access International e-Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A.